# WAMOS 2014

# First Wiesbaden Workshop on Advanced Microkernel Operating Systems

Editor / Program Chair: Robert Kaiser

RheinMain University of Applied Sciences Information Science Unter den Eichen 5 65195 Wiesbaden Germany

Technical Report Februrary 2014

# Workshop Program

| Date:     | Thursday, 13 February 2014                                       |  |  |  |  |

|-----------|------------------------------------------------------------------|--|--|--|--|

| Location: | UdE C Building, C405                                             |  |  |  |  |

| 09:30     | Beginning                                                        |  |  |  |  |

| 09:30     |                                                                  |  |  |  |  |

|           | WINGERT – A Thread Migrating OS for Real-Time Applications       |  |  |  |  |

|           | Alexander Züpke                                                  |  |  |  |  |

| 10:00     | Coffee Break                                                     |  |  |  |  |

|           | Session 1: I/O Support                                           |  |  |  |  |

|           | Session Chair: Thomas Frase                                      |  |  |  |  |

| 10:15     | Supporting USB in a Microkernel Framework                        |  |  |  |  |

|           | Alexander Aring and Timon Link                                   |  |  |  |  |

| 10:45     | A design proposal for a shareable USB server in a microkernel    |  |  |  |  |

|           | environment                                                      |  |  |  |  |

|           | Daniel Ernst and Matthias H. F. Jurisch                          |  |  |  |  |

| 11:15     | Coffee Break                                                     |  |  |  |  |

|           | Session 2: IPC Paradigms                                         |  |  |  |  |

|           | Session Chair: Richard Petri                                     |  |  |  |  |

| 11:30     | Feasibility to replace Interprocess Communication by the Message |  |  |  |  |

|           | Passing Interface in microkernel contexts                        |  |  |  |  |

|           | René Drolshagen and Lasse Löffler                                |  |  |  |  |

| 12:00     | Interprocess Communication (IPC) in comparison to the Message    |  |  |  |  |

|           | Passing Interface (MPI) in a microkernel context                 |  |  |  |  |

|           | Manuel Hermenau and Janos Zweifel                                |  |  |  |  |

| 12:30     | Lunch Break                                                      |  |  |  |  |

|           | Session 3: Scheduling                                            |  |  |  |  |

|           | Session Chair: Matthias H. F. Jurisch                            |  |  |  |  |

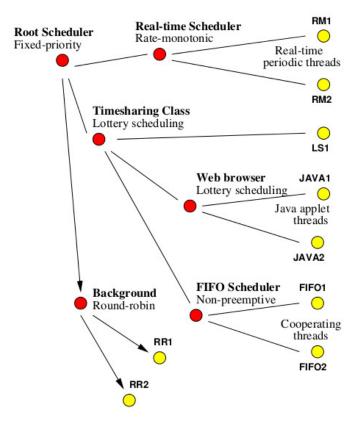

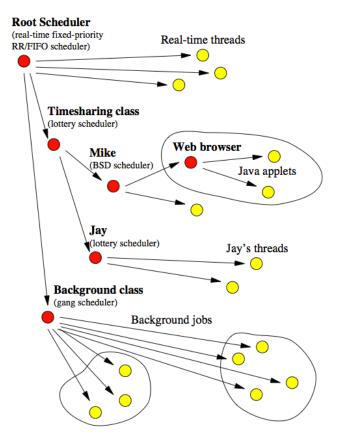

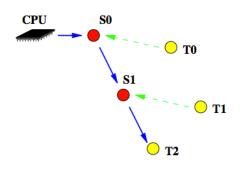

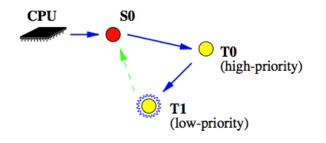

| 13:30     | User-Level CPU Inheritance Scheduling                            |  |  |  |  |

|           | Marcel Kneib and Jonas Reininger                                 |  |  |  |  |

| 14:00     | User-level scheduling mechanisms                                 |  |  |  |  |

|           | Andreas Zoor and Nikolai Nagibin                                 |  |  |  |  |

| 14:30     | Coffee Break                                                     |  |  |  |  |

|           | Session 4: Performance and Isolation                             |  |  |  |  |

|           | Session Chair: René Drolshagen                                   |  |  |  |  |

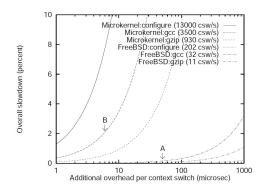

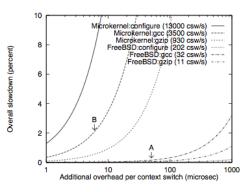

| 14:45     | The long way towards usable IPC Performance in Microkernels      |  |  |  |  |

|           | Richard Petri                                                    |  |  |  |  |

| 15:15     | Side channel attacks in a microkernel environment                |  |  |  |  |

|           | Thomas Frase and Fabian Seiberling                               |  |  |  |  |

| 15:45     | Closing                                                          |  |  |  |  |

|           |                                                                  |  |  |  |  |

# Table of Contents

| WINGERT – A Thread Migrating OS for Real-Time Applications                                                           | 1  |

|----------------------------------------------------------------------------------------------------------------------|----|

| Supporting USB in a Microkernel Framework<br>Alexander Aring and Timon Link                                          | 2  |

| A design proposal for a shareable USB server in a microkernel environment<br>Daniel Ernst and Matthias H. F. Jurisch | 7  |

| Feasibility to replace Interprocess Communication by the Message Passing Interface in microkernel contexts           | 12 |

| Interprocess Communication (IPC) in comparison to the Message Passing Interface<br>(MPI) in a microkernel context    | 17 |

| User-Level CPU Inheritance Scheduling<br>Marcel Kneib and Jonas Reininger                                            | 21 |

| User-level scheduling mechanisms<br>Andreas Zoor and Nikolai Nagibin                                                 | 25 |

| The long way towards usable IPC Performance in Microkernels<br><i>Richard Petri</i>                                  | 29 |

| Side channel attacks in a microkernel environment<br>Thomas Frase and Fabian Seiberling                              | 34 |

# Foreword

The First Wiesbaden Workshop on Advanced Microkernel Operating Systems was conceived to provide a forum for students of the advanced operating systems course at Wiesbaden University of Applied Sciences to present the results of their work.

Besides submitting papers themselves, students also served as members of the program comittee and were involved in the peer-reviewiewing process. The intention, besides the presentation of interesing operating system papers, was to provide hands-on experience in organizing and running a workshop.

The authors were given the opportunity to revise and re-submit final versions of their papers based on the reviews. The papers contained herein are the final versions submitted just before the workshop.

I'd like to thank all participants for their enthusiasm.

I'd like also to thank our guest speaker Alex Züpke who provided an interesting insight into novel concepts of microkernel design.

Robert Kaiser

Program Chair

# **Program Committee**

Alexander Aring René Drolshagen Daniel Ernst Thomas Frase Manuel Hermenau Matthias Jurisch Robert Kaiser Marcel Kneib Timon Link Lasse Löffler Niko Nagibin **Richard** Petri Jonas Reininger Fabian Seiberling Andreas Zoor Janos Zweifel

WiesbadenUniversity of Applied Sciences

# Date: 2014-02-09

# Author:

Alexander Züpke Hochschule RheinMain University of Applied Sciences Campus Unter den Eichen 5 65195 Wiesbaden Germany

alexander.zuepke@hs-rm.de

Title:

WINGERT -- A Thread Migrating OS for Real-Time Applications

# Abstract:

The talk presents the WINGERT research operating system which aims to explore novel OS design patterns for real-time and mixed-criticality systems. Strongly influenced by existing micro kernel designs like L4, we think that a kernel providing a minimal set of abstractions and fast context switches is a key element to achieve high performance and deterministic system behavior.

We present the WINGERT architecture and discuss the use cases of "thread migration" for crossaddress space RPCs (remote procedure calls) in detail to build hierarchical systems on top of this design concept.

Another strong research focus is on resource sharing in such systems: WINGERT provides Futexes (fast user space mutexes) for resource sharing between trusting parties. Untrusting parties utilize thread migration RPC to trusted servers instead. We discuss the benefits of the locking architecture in detail.

# Supporting USB in a Microkernel Framework

[Extended Abstract]

Alexander Aring Hochschule Rhein-Main University of Applied Sciences Kurt-Schumacher-Ring 18 Wiesbaden, Germany alex.aring@gmail.com

# ABSTRACT

This paper provides an introduction in supporting USB in a Microkernel-Framework. In order to understand the main thoughts, a quick overview about the USB-specification is provided. Microkernels have a small trusted code-base, so the major part of the USB-Framework has to been implemented in userspace which is the USB-drivers themselves and the UHCI. The several USB-drivers has to cooperate with each other or the UHCI by exchanging messages. The task of sending and receiving messages is handled via IPC. This leads to a bottleneck by communicating to the kernel, because each IPC is realized as a system call. In case of *HelenOS*, a microkernel operating system we choose to use as example, a solution is provided by reducing the communication overhead.

#### **Keywords**

USB-Stack, USB, USB-Framework, Microkernel, HelenOS

### 1. INTRODUCTION

20 years of microkernel and 19 years of universal serial bus. It's time to marry these two technologies together. This paper describes an example implementation of an USB framework inside microkernels.

#### 2. PURPOSE

This paper describes an USB framework for microkernel systems. Additional the USB framework will keep the microkernel philosophy.

#### **2.1** Idea

We use the idea of microkernel and build an USB framework on top. An USB microkernel framework has several service

\*B.Sc. in Computer Science

<sup>†</sup>B.Sc. in Computer Science

Timon Link Hochschule Rhein-Main University of Applied Sciences Kurt-Schumacher-Ring 18 Wiesbaden, Germany timon.link@gmail.com

applications. These services will handle the USB framework and abstract a generic USB interface to interact with applications which use the framework.

#### 2.2 Problem

The USB framework sevices need a complex mechanism to handle the necessary USB functionality. This paper describes the necessary complex mechanism to solve this problem.

### 3. USB SPECIFICATION

USB stands for Universal Serial Bus and is developed by Intel Corporation. Today (in year 2014) this bus system is the most common used peripheral bus system for desktop pcs. The term "peripheral bus" describes a bus system to provide a wide support for a wide variety of devices. These devices can be a keyboard, mouse, etc. USB supports hotplugging. This means an USB device can be added or removed during runtime. In this paper we use the USB specification 2.0 [Cor00] to get a basic information about USB.

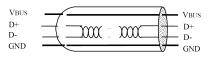

There are several kinds of USB port connectors to connect an USB device into USB. This connectors provide the same physically background inside the USB cable. The only difference is the form factor of an USB connector. USB uses a differential voltage for signaling. The USB Cable on USB 2.0 and backwards has four wires.

Figure 1: Wires of an USB cable. [Cor00]

Figure 1 shows the USB cable wires. The data wires are twisted to reduce signaling failures from electromagnetic fields. The other two wires are there to provide a five volt power supply and ground. Newer USB 3.x specifications have more than one twisted data wire to provide a higher bandwidth. Each USB specification describes how an USB cable needs to be build to provide the USB specification conditions.

The first USB 1.0 specification was released in November 1995. Since then Intel released USB 1.1, 2.0, 3.0 and 3.1

specifications. Each of them is backwards compatible to the previous USB specification.

### 3.1 USB Device

An USB device is usually a peripheral device like a keyboard, mouse, printer, video, storage, etc. This device offers an USB connector and the internal firmware of the device follows an USB specification.

#### Figure 2: Certification logo of USB 3.0 Standard. [Wik14c]

Figure 2 shows an example of the USB 3.0 certification logo. Only USB 3.0 certification devices can use this logo.

#### 3.1.1 Classes

The USB specification describes a wide area of USB device classes. In this paper we handle with the following USB classes: HID (human interface device), UVC (USB video device class) and MSC (mass storage).

Each USB class has an unique identifier in the USB specification. If an USB Device doesn't fit in any USB class like a fancy USB lamp, there also exists a vendor specific USB class. An USB class provides a generic interface to interoperate with a generic USB device class driver. For example a BIOS does provide a generic HID driver to interoperate with a connected USB keyboard. The generic HID interface is specified by the used USB specification.

#### 3.1.2 Descriptors

An USB device knows what functionality it offers. Besides the functionality it knows the consume of his power supply. These information stands in the descriptor table of an USB device. The firmware contains the descriptor table and provides this information. It's necessary that an USB device provides a descriptor table. The descriptor table contains the following kinds of descriptors:

- **Device Descriptor** Contains general information about the connected USB device like the device class. Every USB device has only one device descriptor.

- **Configuration Descriptor** Contains information about the configuration of the connected USB device. There also exist a way to configure an USB device at runtime if necessary.

- **Interface Descriptor** Describes a specific interface with a configuration. An interface provides zero or more endpoint descriptors.

- **Endpoint Descriptor** An endpoint is a communication channel to send or receive data to or from an USB device. Each endpoint has a number to identify the endpoint.

The device descriptor contains two important information about the USB device.

- **VID** Stands for Vendor ID. A company which will produce an USB device needs a registered ID. The VIDs are managed by Intel.

- **PID** Stands for Product ID. Each different USB device which is produced by a specific company needs a Product ID.

A combination of VID and PID provides an unique identifier for any USB device.

# **3.2 Endpoint Transfer-Types**

All transfer messages on USB has little endian encoding. An endpoint descriptor has a transfer type to describe the kind of message which is provided at the specific endpoint. The USB specification has four kinds of transfer types, which are:

- **Control** Control transfers are used to get or set configurations, commands or statuses of an USB device. This type of transfer is used in all kind of USB devices.

- **Bulk** A bulk transfer provides a large data transfer support. This is usually used in mass storage devices which require a high bandwidth. Common used in MSC class devices.

- **Isochronous** Like a bulk transfer type but provides a guarantee of required bandwidth. Common used in UVC class devices.

- **Interrupt** This kind of interrupt isn't an interrupt in an usually case. An interrupt transfer type provides a periodically request of small data. Common used in HID class devices.

There exists a special endpoint with the number 0. An USB device must have this endpoint. This endpoint offers a control transfer type. Over this endpoint the descriptor table is accessible to enumerate devices on the USB system.

# 4. USB HOST CONTROLLER

An USB host controller is an electrical hardware chip. Each pc which supports USB has an USB host controller inside the northbridge on a desktop pc. This chip handles some USB operations on hardware. These operations are some time critical operations which cannot be handled by software. The operations and interfaces are specified by a host controller interface standard. There are four different host controller interface standards. These are OHCI, UHCI, EHCI and XHCI. The USB host controller doesn't implement the full USB specification. On top of an USB host controller driver must run an USB implementation. This implementation is usually known as USB stack.

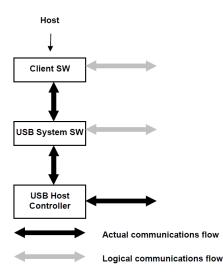

Figure 3 shows the architecture model of an USB host controller, USB stack (described as USB System SW) and an USB driver (described as Client SW). These three layers are usually involved to run an USB system.

Figure 3: Host Composition. [Cor00]

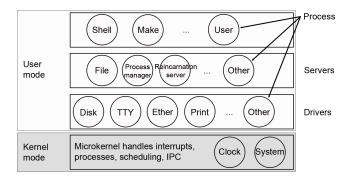

# 5. MICROKERNEL

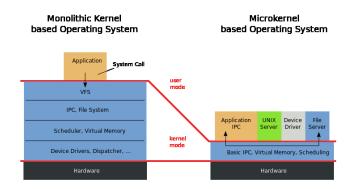

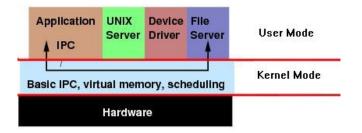

A microkernel  $(\mu$ -kernel) aims the goal, as against the monolithic kernels, to store the minimum amount of functionality in the privileged mode, which are needed to run an operating system. The functionality is reduced to inter process communication (IPC), thread management and memory management. As the monolithic kernels also implement the device drivers, filesystems and other components, microkernels only implements these software as userspace programs. This reduces the Lines Of Code (LOC) up to 10.000 [KE13, sec. 2] in the seL4 kernel. The advantage of the small amount of LOC is the reduced error-proneness. This prevents the microkernel to crash as often as a monolithic kernel, because most of the functionality is implemented in userspace. When an userspace program crashes, e.g. a device driver, it will be simply restarted without taking effect on the kernel runtime. Figure 4 shows the principles of a monolithic kernel vs. microkernels.

#### Figure 4: Structure of monolithic kernel vs. microkernel [Wik14b]

In both approaches an userspace program invokes a *system* call to get access to a needed functionality from the kernel. In case of *Unix*, the amount of system calls is 40 [hl14], whereas the L4 gets along with only 10 system calls [hcl14].

The main concept goal of microkernels is to store the most functionality in userspace. This leads to the concept of *client-server-communication*. Both, the server and client, are running in userspace. A server can be imagined as a daemon process, which offers a special service, e.g. a filesystem service, to consumers which are the clients. The server handles the communication with the microkernel by using system calls. The communication between server and client is handled by *IPC*, which will be described in detail in chapter 5.3 *Inter Process Communication*.

#### 5.1 Related Microkernels

This section gives a short overview of existing microkernels with the main concepts and ideas in their chronological order.

- Mach This Microkernel was developed by Carnegie Mellon University at 1985 [CMU14]. It's often mentioned as the pioneer of microkernels and so it's seen as the first generation. Mach abstracts the *pipe* of Unix by using IPC. The developer introduced the concepts of *tasks* which are sets of system resources, *threads* - a single unit of execution, *ports* as a message queue for IPC between tasks and *messages* which are a collection of data objects to send to the different ports. But IPC is also the bottleneck of Mach. It slows down the kernel up to 50% compared to a native Unix implementation.

- Minix 3 Minix 3 [Min14] was developed by Andrew S. Tanenbaum and released in 2005. The motivation behind this microkernel is security, flexibility and high reliability. It's the second generation of microkernels.

- L4 This Kernel was developed by Jochen Liedtke as replacement of L3. The main idea is a well designed, reduced IPC layer to eliminate the bottleneck of IPC known in Mach. Liedkte has written the source code in pure i386 assembly language. With this implementation Liedtke revolutionised the family of microkernels. Many research centres and universities began to implement the L4 Kernel in high level programming languages. Popular results are the L4Ka::Hazelnut, L4ka::Pistachio (both developed at the University of Karlsruhe), L4/Fiasco from Dresden University of technology, OKL4 and seL4 both impelled by Gernot Heiser.

#### 5.2 Processes

In the context of operating systems (OS) there exist two kinds of processes. The processes in kernelspace and processes in userspace. Userspace processes don't have the permission to interact directly with the hardware of the underlaying platform. As mentioned before in section 5, microkernels only implement the minimum amount of functionality as processes in kernelspace, which are needed to run an operating system. But there are a lot of services of an OS, which need to interact with the underlaying hardware, e.g. a filesystem or a systemtimer. These services don't run in the privileged kernelspace, which would hurt the principles of a microkernel. So they have to be implemented in userspace. This causes us to take a closer look to the userspace processes. Userspace processes are typically split into two parts, server and clients. Servers offers a special functionality, by interacting with the kernel via system calls, to the clients. The communication between servers and clients is handled by a RPC-type Inter Process Communication IPC, which is described in detail in section 5.3 Inter Process Communication.

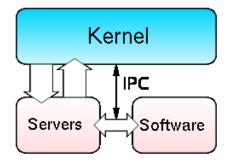

Figure 5: Principles of client-server [Wik14a]

Figure 5 shows the concept of client and server communication. In this case the client is simply called *software*. In fact there is no technical difference between servers and clients, so servers are software too.

#### 5.3 Inter Process Communication

Inter Process Communication *IPC* allows separate Processes to communicate via messages. This concept is the premise for the client-server model described in section 5.2. Without IPC it would not be possible to strictly divorce the clients from servers and the most hardware near software like device drivers had to been implemented in privileged kernelspace.

There are two concepts of IPC - synchronous and asynchronous.

- **synchronous** Synchronous IPC forces the sender and receiver to block the execution of the program and wait for the other side to perform the IPC. When the IPC was performed the execution can be continued. There is only one decision for the programmer, either to implement an *infinity-timeout* or a *zero-timeout* for the waiting, if a deadlock occurred and the IPC can't be performed.

- **asynchronous** Asynchronous IPC is analogous to known concepts of network communication. The sender sends a message and continues executing. The receiver waits for the message by polling the sender. But this forces the kernel to maintain buffers for messages. This is the bottleneck of older microkernels which Liedkte has discovered. So he chooses to ban asynchronous IPC from his L4 implementation.

In most microkernels is only support for synchronous IPC integrated, to prevent the performance issues. But this is going to cost the comfort of the programmer, because he has to handle the rendezvous of both sides manually.

### 6. MICROKERNEL USB-FRAMEWORK

In this section we give a detailed overview about the required features to support *USB* in microkernel-based operating systems. The main challenge is the design of an USB framework inside the microkernel-architecture. This chapter discusses a working USB framework based on the example of *HelenOS* [hel14].

#### 6.1 Related Microkernel USB-Stacks

In the following section we will show the example of an existing operating systems, based on a microkernel, which supports *USB*.

#### 6.1.1 HelenOS

HelenOS aims the goal to be a very portable OS. At the moment HelenOS only supports USB 1.1 with keyboards and mice, but it worth to take a closer look to the principles of implementation. The USB subsystem [hel14] in HelenOS consists of these thoughts:

- drivers for host controllers

- drivers for USB devices

- mechanism to start device drivers when hotplugging occurred

- allow client programs to use the plugged in devices

- drivers have to communicate with each other

HelenOS offers a great feature to achieve the last three goals, the HelenOS *Device Driver Framework DDF* [hel14]. This generic framework is used by developers to implement specific device drivers. In fact that the framework supports the features

- start drivers automatically,

- driver to driver communication and

- offer a layer for exposing device interfaces to client programs,

it's a good idea to use it as backend for building USB device drivers. This offers a great advantage for implementing USB device drivers, because each driver is a standalone task that communicates with other tasks (drivers or clients) through IPC. The meaning is, that complicated drivers could be built modulary by splitting the driver in multiple tasks which cooperate with each other. So the effort of maintaining the driver is reduced and also the number of bugs of each partition.

The cooperation of multiple drivers is used in HelenOS for the implementation of the *UHCI* (host controller driver). The developers decided to split this driver in two tasks. One driver for the UHCI itself and a second driver as *OHCI* (hub controller) driver and for the root hub. The *UHCI* and *OHCI* are strictly coupled. That means, if one driver is not started or has a failure, the other doesn't work at all. Another meaningful usage of the coorperation are *multiple interface devices (MID)*. These (USB) devices support several interfaces to access the functionality of the device. A good example for a MID are digital cameras. One way to access the photographs is through a specific vendor interface, which needs a special driver. As fallback solution, when the vendor interface crashes or is simply not supported, digital cameras can be accessed via a mass storage driver. These two capabilities would be implemented in two drivers, which cooperate via DFF to support one MID.

The next step to understand the USB subsystem in HelenOS is to take a closer look to the USB devicetree.

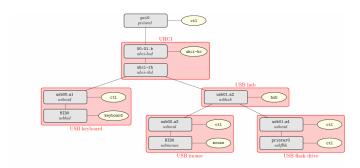

Figure 6: Example of devicetree in HelenOS [hel14]

Figure 6 shows an example of a possible scenario, when an USB hub, an USB keyboard, an USB mouse and a printer are connected to the host controller *UHCI*. In order to explain the concepts of the devicetree it's only necessary to describe some parts of it, because all connected devices work in a similar way. The first component to look at ist the host controller. The UHCI offers a function called *uhci-hc* which is invoked by all connected drivers to register the device. The host controller then connects all registered devices directly to the PCI-bus.

The leaf USB keyboard represents a connected keyboard device, which is obviously a MID. As mentioned before MID drivers are split into tasks - two in this case. When the device is plugged in a generic Human Interface Driver (HID) starts up. The main task of this driver is to capture key events and send them to connected clients. Clients in this context are processes which consumes the key-inputs from the keyboard driver.

The second driver is the MID-driver. It handles the communication between the device and his parent- and childrenleafs by offering a special function ctl. Below the communication inside the devicetree is described in more detail.

The concept of the communication inside the tree is leaning on *parent-only* communication, which means that drivers can only communicate with their direct parents. The advantage of the parent-only communication is the exact adaption of the physical topology to the virtual device tree. But a big disadvantage is the performance. Let's examine a scenario, when the mouse is plugged in to the above devicetree (see Figure 6). The following Figure 7 shows the principles of the communication in this scenario.

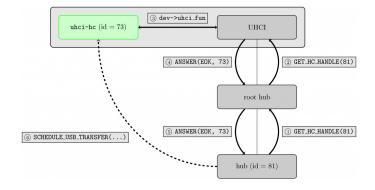

Figure 7: Communication scenario [hel14]

At first the mouse is plugged in and the MID driver starts. At this point the driver tries to register at the UHCI, but it only has the possibility to contact it's direct parent, which is in this case the *root hub*. So the MID driver asks the root hub for an *UHCI*-handle. But the root hub isn't the UHCI and has to forward the request to his direct parent. This scenario repeats until the UHCI is reached. The UHCI then answers the request and sends his answer over all leafs to the MID driver of the plugged in mouse. Obviously an *USB transfer* within the same concept is an enormous overhead and would slow down the transfer itself. But since the MID driver and the UHCI has exchanged their ids, the transfer is handled by a function *SCHEDULE\_USB\_TRANSFER*, offered by UHCI, directly called by the MID.

# ADDITIONAL AUTHORS REFERENCES

- [CMU14] CMU. Overview of the mach project, January 2014.

- [Cor00] Intel Corporation. Universal Serial Bus Revision 2.0 specification. Compaq, Hewlett-Packard, Intel, Lucent, Microsoft, NEC, and Philips, 2.0 edition, April 2000.

[hcl14]

http://www.cse.unsw.edu.au/ cs9242/07/lectures/02 l4x6.pdf. L4 programming introduction, Janurary 2014.

- [hel14] helenOS. Usb subsystem in helenos, January 2014.

- [hl14] http://www.di.uevora.pt/ lmr/syscalls.html. Unix system calls, Janurary 2014.

- [KE13] Gernot Heiser Kevin Elphinstone. From l3 to sel4 what have we learnt in 20 years of l4 microkernels? NICTA, UNSW, April 2013.

- [Min14] Minix. Minix 3, January 2014.

- [Wik14a] Wikipedia. Kernel (computing) Wikipedia, the free encyclopedia, 2014. [Online; accessed 20-Janurary-2014].

- [Wik14b] Wikipedia. Microkernel Wikipedia, the free encyclopedia, 2014. [Online; accessed 19-Janurary-2014].

- [Wik14c] Wikipedia. Universal serial bus Wikipedia, the free encyclopedia, 2014. [Online; accessed 23-Janurary-2014].

# A design proposal for a shareable USB server in a microkernel environment

Daniel Ernst Hochschule RheinMain Fachbereich Design Informatik Medien Unter den Eichen 5 D-65195 Wiesbaden daniel.ernst01@gmail.com

#### ABSTRACT

The Universal Serial Bus has gained importance on the desktop market in the last years. Nowadays, even systems like the Raspberry Pi use them for tethering different peripherals. When building a shared USB server in a microkernel environment problems like controlling access-restrictions and scheduling bus access are important. It is also unclear, how such a system should encapsulate the USB access.

In this paper we will compare different approaches for solving these problems. Due to the universal purpose of this bus-system, we will illustrate an application- scenario which will address both real-time- and a multimedia-applications simultaneously. We will focus on the main-problems in such an environment. The first will be how the access to the bus can be restricted and which patterns are suitable for our application-scenario. The second will be how the bus can schedule the communication while assuring the real-timeability. Different algorithms will be discussed. Finally, different design ideas for the server interface will be compared while targeting to retain existing implementations. From this discussion we will propose a design for a USB driver server and discuss its strengths and weaknesses.

#### **Keywords**

Microkernel, Universal Serial Bus, Shared Resource, Realtime, libUSB, Scheduling, Access Rights Management

#### 1. INTRODUCTION

Microkernels in general allow a secure isolation of different applications running on them [5]. The separation of policy and mechanism makes it possible to decrease the size of trusted code which makes it easier to build safety-critical applications.

When mixing safety-critical applications with conventional applications without security implications, the isolation of microkernels allows these applications to run on the same Matthias H. F. Jurisch Hochschule RheinMain Fachbereich Design Informatik Medien Unter den Eichen 5 D-65195 Wiesbaden matthias.jurisch@gmail.com

computing node. When there is no need for sharing any resources, a reasonable configuration of the microkernel will usually even allow the safety-critical application to work properly when the conventional application misbehaves.

If the applications share a resource, some kind of mechanism has to be provided for sharing this resource and protecting it against denial-of-service-attacks (DoS). Simply allowing all applications to access the resource will not be a sufficient solution. This can be done by implementing another application that acts as a server for the other applications when they try to access the shared resource. For making the resource accessible, the server will send and receive messages through the inter-process-communication-mechanism of the microkernel.

The Universal Serial Bus (USB) is a very popular bus system for accessing peripherals. It is quite common that a lot of peripherals are attached this way. This will turn the USB into a shared resource, when different applications need to access different peripherals that are made available through the bus.

Since it is very common to use the USB as a shared resource, a sufficient mechanism for sharing is needed. In this paper, a design for this kind of mechanism will be provided. The sharing itself will lead to two questions:

- 1. Which USB transaction can be excecuted when?

- 2. How will access permissions for devices be checked?

In chapter 2 a quick overview of USB is given. Chapter 3 will provide a short application scenario. A general overview of implementing USB support in microkernels is given in chapter 4. Ideas on how to solve the problem 1 are discussed in chapter 5. Chapter 6 describes solutions for problem 2. A design overview over the server is given in chapter 7.

# 2. USB

The Universal Serial Bus [10] is a serial bus system widely used on the desktop market. It is used for different tasks such as tethering peripherals in PCs, as powering gadgets like a fondue pot. USB is standardized by the USB Implementers Forum; the current version of the standard is V3.1, published in 2013. The bus is strictly hierarchical and host-centric, this means every information exchange will be routed through the host. This can be seen in the design of the USB connectors. The connector type A (see figure 1a) always faces towards the *host* and the connector type B (see figure 1b) always faces towards the *device*.

Figure 1: USB connectors

The descriptor hierarchy in the USB specification is a very important concept from a software point of view. Descriptors allow to get information from a USB device about what kind of device is the current one, what configurations are available and what configuration endpoints can be used. Therefore, there are *device desriptors* containing *configuration descriptors* that contain *endpoint descriptors* themselfs that contain *interface descriptors*.

The device descriptors contain the information describing the device, for example the *Vendor IDs* and *Product IDs*. These device descriptors also contain information about the device's *device class*. A device class specifies the type of device, for example keyboard, storage device and other device types are possible. By providing a default driver for these device types, they can be supported without a special driver provided by the manufacturer, given, the device follows the device specification properly.

For the configuration definition, the configuration descriptors are used. Endpoint descriptors describe the endpoints, that can be used as endpoints for communication. Every endpoint is the end of a unidirectional pipe to the USB host. IN-endpoints are used to send information to the host and OUT-endpoints are used to obtain messages from the host.

For the data transfer there are four different transfer types:

- Control transfer: This transfer type is used to exchange status information or similar data.

- Interrupt transfer: This transfer type should be used to send urgent data, since it has a guaranteed latency.

- Isochronous transfer: This should be used for periodic data transfer, for example for video streams. This transfer type guarantees a certain bandwidth.

- Bulk transfer: When transfering large amounts of data without time restrictions, this transfer type should be used.

# 3. APPLICATION SCENARIO

For a better understanding of the problems that arise from using the USB as a shared resource, we will provide a short application example. In the automotive industry, the trend is going towards Androidbased media centers in cars. If we want to use this Android media center as a computing node for real time data processing of a sensor communicating via USB, we need some kind of architecture that supports the sharing of the USB.

We consider the following example: A media-center in a car is running Android. The installation of user-provided apps is allowed. It is possible to connect mp3-players via an USB slot and use them as storage devices to play music. Additionally, a tachometer is attached via USB to the media-center, to gather the mileage information.

To prevent malicious apps to change the mileage data and to interfere with the data from the tachometer, we need a microkernel based system, that runs the Android system as one task and the real-time application as the other. In this way, changing the mileage data from the Android system is not possible. The only problem that remains is how to share the USB between the Android system and the real time mileage application.

### 4. THE USB-SERVER

To approach this problem we first have to take a look at what is needed to provide USB support in a microkernel environment. Sharing access to the USB hardware for all applications running in the microkernel environment is considered a bad idea, because there could be conflicts between the several applications that access the bus. Therefore, implementing a server that encapsulates the required USB functionality is a better choice. To get a short overview of what is generally required, we will briefly discuss the USB-driver approach in the Linux kernel.

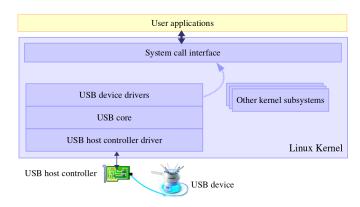

In the Linux kernel (see figure 2) there are three layers of USB drivers:

- 1. The host controller driver, which provides access to the host controller hardware that controls the USB

- 2. The USB core, that helps higher level drivers access the bus system and

- 3. USB device drivers, that provide support to several USB devices.

Figure 2: USB drivers in Linux[8]

When an USB device driver tries to send data to the device it handles, this is done through USB Request Blocks (URB) [6]. An URB encapsulates all information that is required to do a complete USB transfer.

The straightforward approach to supporting USB in a microkernel would be to implement a server containing the layers 1 and 2 of the Linux USB stack. The server can receive URBs from different client applications and forward these transfers to the USB. Layer 3 would be implemented by different client applications that have access to the server and send him URBs.

If we follow this architecture, we can identify two problems:

- 1. How can we decide, which URB should be processed next, so that no DoS attacks against the USB server are possible?

- 2. How can we restrict access to the bus so that only trusted applications can read and write from safety/security relevant devices?

If we reconsider the application example, we can see that when no sufficient solution for the first problem is provided, it will be possible for an Android app to spam the USB so that no mileage data can be received by the real-time application. If no solution for the second problem is provided, it might even be possible for a malicious android app to send commands to the mileage data sensors and disable them or bring them to an inconsistent state. In the following chapters we will discuss solutions for these two problems.

#### 5. BUS ACCESS SCHEDULING

For using shared resources, we have to define who will be the next to be granted access to this resource. This is called scheduling. The easiest solution for this problem is to simply use a first-come-first-serve algorithm for all clients. This could be implemented through a simple FIFO-datastrucure. If we think of the application example, this is problematic. A malicious Android app could submit lots of URBs and therefore block the real-time-applications access to the bus. This could result in the real-time application not receiving the mileage data. Even the real-time application itself could be threatened. Urgent URBs might be submitted later than non-urgent URBs. This could result in the urgent URBs being sent later than when they are due.

Therefore, we will compare several scheduling algorithms for real time scheduling. A very popular scheduling algorithm in this domain is *earliest deadline first* (EDF) [7]. The idea of this algorithm is to add a *deadline* to each task. The deadline describes at what time a certain task has to be finished. The next task to be started is the task with the closest deadline. It can be proven that preemptible EDF is an optimal algorithm when scheduling for a single resource. It can even be proven that if an EDF schedule fails to comply with a deadline, no solution that complies with all deadlines is possible. Since not all tasks have a deadline, finding sufficient deadlines can be problematic.

Another quite important algorithm is *least laxity first* (LLF) [4]. This scheduling algorithm calculates the laxity l with

deadline d, remaining task execution time c and current time t, determined by

$$l = (d - t) - d$$

which can be seen as the time that can pass until the task has to start. The task with the smallest laxity l is the task, that is executed first. LLF can be proven to be optimal for scheduling for more than one ressource. It is not applicable in our case, because we don't quite know the execution time c. Also, for tasks with equal execution time LLF behaves exactly the same as EDF. It is reasonable to assume, that processing URBs has a quite similiar execution time.

Fixed priority scheduling[1] assigns each task a fixed priority. The task with the highest priority is scheduled first. Scheduling algorithms for periodic tasks like RMS [7] are not covered here, since we are not dealing with periodic tasks.

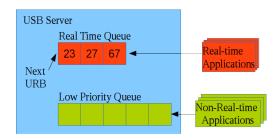

For our problem, we will regard the USB host controller as the resource that is scheduled. The tasks to be scheduled will be the single URBs to be sent. A possible solution for efficient host controller scheduling would be to use EDF for scheduling the URBs. Every URB has an attached deadline. Non-urgent packages could be attached a deadline infinitely in the future. In this case, a misbehaving client could still block the bus by submitting URBs with very close deadlines. This could be fixed by a static configuration that is read by the USB server at startup. In this configuration, the applications that have to use real-time features could be listed. These could be the only applications that are allowed to set the deadline of an URB. All URBs sent by other applications will have a deadline infinitely in the future, these would be scheduled with a FIFO algorithm.

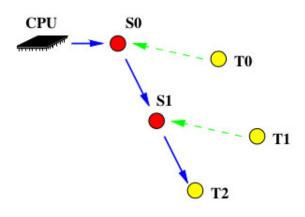

For providing a different scheduling algorithm for the nonreal-time applications, two queues could be provided. One (with a high priority) would be scheduled with an EDF algorithm and conatins only URBs by privileged real-time applications. The other queue (with low priority) would contain a queue of non-real-time URBs; this queue could be scheduled with any non-real-time scheduling algorithm. This design can be seen in image 3. The numbers in the orange squares represent the deadline of the URBs.

Figure 3: Scheduling with two queues

#### 6. ACCESS RIGHTS MANAGEMENT

The application scenarios in chapter 3 show that having multiple applications and multiple USB-devices can be dangerous, especially if a sensitive environment is concerned. The access of applications to USB-devices need to be restricted and managed by the system in order to prevent a failure or even a malicious threat to harm the sensitive environment. The proposed USB-server as the only module to access the USB-host of the system stands between the potential misuse of applications on USB-devices. Therefore it needs to manage which applications may make use of which devices.

Let us say that the USB-devices to be protected are objects, then pairs of objects and rights can be called domains. The system needs to know any domain combined with any object to make a decision. The result can be seen as a table, where e.g. the rows are domains and the columns are the objects. Each box in the table then holds the rights between the specific domain and the corresponding object. This table is redundant, since many combinations of domains and objects do not have any entries. By declaring that every empty cell of that table means that there are no access-rights between this domain and the object (*white-listing*), the redundancy can be minimized. Also, the principle of least privilege is maintained. Finally this table can then also be seen as a list of domains, where each domain holds a list of objectright-pairs (called *capabilities*), or as a list of objects, where each object holds a list of domain-right-pairs (called Access Control Lists (ACL)) [9].

In an ACL each object (the USB-devices) holds a list of domains (the applications) and which rights they provide, like read and write on the devices. This list will be queried each time a domain wants to access an object. Unlike the ACLs, capabilities are domain-driven. That means that each domain will hold a list of objects and the information on how it may access these objects. Therefore, the concepts of ACLs and capabilities can be seen as complementary.

The ACL and the capabilities both have their advantages and disadvantages. The capabilities are efficient; using generic rights, like copying and inheriting a domain's capabilitylist, provide a top-down-structure where access-rights can be controlled for subdomains. On the other hand, if an object's rights need to be revoked system-wide, e.g. because the object is removed, each domain's capability-list concerning that object must be reconsidered. If then an object is being removed without revoking all domain's rights beforehand, orphan-rights may occur and lead to even more problems. Since in an ACL any object holds their own list of domain-right-pairs, this problem doesn't occur there. But having many domains will cause the ACLs to grow very long, thus making finding, inserting and deleting items in this list less efficient [9].

But even though the capabilities provide some very useful features, there occurs a major problem for our case. The concept of capabilities is that the access to an object is granted purely on the mere possession of a capability. An application must therefore obtain and use their capability on accessing an USB-device, and therefore the application's code has to be adjusted. Practically, many changes on the APIs would be needed. ACLs on the other hand can be used in a centric and isolated USB-server-module. Every time an application wants to access a device via the USB-server, the server will query its ACL and decide whether or not this query will be granted. In our use-case it is stated that there are a few, very distinct applications but multiple, also very distinct USB-devices. But USB-devices like thumbdrives can be added to the system on runtime (hotplugging) and they may be completely unknown to the system beforehand. On the one hand, the system needs to react to an arbitrary USB-device and give the applications access-rights. Following the principle of least privilege mentioned above, any newly added device which was unknown a priori will therefore not be accessable by applications at all. This leads to the question, how the access-rights are created and provided for hotplugged devices. Obviously there is a wide range of different USBdevices which can't all be known beforehand. Furthermore, providing basic rights in general is a security threat, while not providing any rights to hotplugged devices renders them useless and therefore isn't an option either. Our use-case states that both types of applications need to be handled at best; e.g. a real-time-safety device as well as a multimediaapplication based on Android. While the safety-devices have our priority in this paper, the usability of an USB-thumbdrive containing music-files still needs to be as good as possible.

While there are plenty of possibilities to authenticate USBdevices and applications, like a key-system, there will always be the need to adjust the system more or less, e.g. that every USB-device needs an authenticating key through which basic access-rights can be determined by the USB-server. This will render any *unprepared* USB-device useless, thus making a plug-and-play of an arbitrary USB-thumbdrive containing music-files impossible. Therefore another option is to create a configuration which will be read on boot. It will determine which applications have which rights on which USB-device. While not all different devices can be covered, groups of devices can. Using the USB device descriptors (see chapter 2), classes and subclasses (like mass-storage-device) can be used to group unknown devices and provide basic access-rights to the applications. Additionally the vendor- and product-IDs can be used as well. This way, common USB-devices like thumbdrives can still be used when hotplugged, while critical devices can still run safely. Adding group-rights to the concept of ACLs basicially equals a minimal Role Based Access Control model (RBAC) [2].

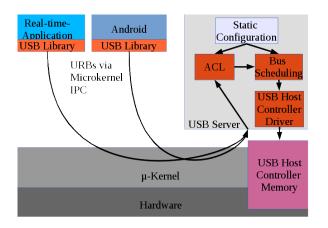

# 7. SERVER DESGIN

The implementation of USB support in a diversified and heterogeneous environment can be realized with a server that solely receives URBs. The desgign can be seen in figure 4. The URBs are processed by the server and forwarded to the USB controller hardware. This has the advantage, that porting e.g. linux drivers for USB devices can be quite easy. When running a linux kernel on top of the microkernel, a pseudo driver that simply sends URBs to the USB server can be implemented. All existing USB device drivers for the linux kernel can be reused.

After an URB has been sent to the server, it is checked whether the client sending this URBs has sufficient rights for performing this operation. The rights are realized based on the concept of ACLs described in chapter 6. On boot, for each plugged-in USB-device the respective Access Control Entries (ACE) will be created based on the definitions in the static configuration. These will most likely include critical USB-devices who e.g. need to run in real-time. When

Figure 4: Architecture of the proposed server

an USB-device is hotplugged — e.g. USB-thumbdrives and the like — the server will determine the respective ACE by reading the static configuration again. The configuration can contain rights for explicitly stated devices by device-ID, or group-like rights for multiple unknown devices through using device descriptors. If then the application is sufficient to access the device, it will be granted. If no sufficient rights can be determined for the application, the access will be denied and any URB sent to the server will be ignored.

After having passed the ACL, the URBs can be submitted to the bus scheduling module, that applies a scheduling algorithm described in chapter 5. This component then decides, which URBs should be processed next and accesses the USB master controller hardware. This can be done by accessing the USB device controller io hardware provided by the microkernel.

#### 8. CONCLUSIONS

In this paper we have discussed a design-pattern for a shareable USB-server based on microkernel-architecture. The application scenario is focused on a heterogenous and diversified environment, where critical, possibly real-time USBdevices and user-friendly mulimedia devices both need to be addressed. The critical real-time devices are granted a priority here, whereas the less critical ones need to be treated as good as possible.

The main issue is that non-real-time components can interfere with the real-time-components maliciously. Therefore we figured that the biggest threats on this shared USB-host concern the bus-scheduling as well as the access-management. Additionally, we focused on making the least possible changes to the environment, so that no changes on neither the USBdevices nor the applications (e.g. USB-drivers) are needed.

Providing access to the bus is done by submitting URBs to a USB server, that then forwards the requests to the bus. The provided solution will allow the leveraging of existing Linux driver code, since this approach uses URBs, just as linux USB device drivers. Also, a host controller driver for a Linux VM that accesses the server can be easily implemented, because this driver would simply need to forward URBs.

Providing a real-time-ability without being harmed by nonreal-time components is reached by mixing priority based and deadline scheduling. The solution is working well, when there is only few real-time activity. Intense activity of realtime based applications will basically exclude non-real-time applications from the bus.

By using the concept of ACLs and the principle of least privilege, the access to USB-devices can be restricted. Due to the wide range between real-time-ability and consumer-usabilty, tradeoffs had to be made. While whitelisting cancels out unknown and therefore possibly malicious devices in general, the static configuration allows an administrator to explicitly grant access to hotplugged devices. Using USB-device descriptors for device-classifications adds to the usability. But granting general access-rights to the system lowers the security-level, e.g. by using adjusted USB-devices and applications. This ultimatively means that the administrator of this implementation needs to adjust the security-level to his needs, starting at highest security and lowest usability as default configuration.

#### 9. **REFERENCES**

- N. Audsley, A. Burns, R. Davis, K. Tindell, and A. Wellings. Fixed priority pre-emptive scheduling: An historical perspective. *Real-Time Systems*, 8(2-3):173–198, 1995.

- [2] J. Barkley. Comparing simple role based access control models and access control lists. In *In Proceedings of* the second ACM workshop on Role-based access control, pages 127–132. ACM Press, 1997.

- [3] Beyond Logic. USB in a Nutshell. http://www.beyondlogic.org/usbnutshell/usb1.shtml, 2014.

- [4] M. L. Dertouzos. Control robotics: The procedural control of physical processes. In *IFIP Congress*, pages 807–813, 1974.

- [5] P. Hansen. The nucleus of a multiprogramming system. Communications of the ACM, 13(4), 1970.

- [6] Linux Kernel. Usb request blocks. http://freeelectrons.com/kerneldoc/latest/usb/URB.txt, 2009.

- [7] C. L. Liu and J. W. Layland. Scheduling algorithms for multiprogramming in a hard-real-time environment. J. ACM, 20(1):46–61, Jan. 1973.

- [8] M. Opdenacker. Linux usb drivers. http://free-electrons.com/doc/linux-usb.pdf, 2009.

- [9] A. S. Tanenbaum. Modern operating systems. *Prentice Hall PTR*, 2, 2001.

- [10] USB Implementers Forum, Inc. USB Standard Version 3.1. http://www.usb.org/developers/docs/, 2013.

# Feasibility to replace Interprocess Communication by the Message Passing Interface in microkernel contexts

B. Sc. René Drolshagen Wiesbaden University of Applied Science Department DCSM Unter den Eichen 5 Wiesbaden, Germany info@rene-drolshagen.de

#### ABSTRACT

The dominant male in the last 35 years of microkernel development was the Interprocess Communication (IPC). Since the day microkernel came up, using IPC as the message passing model was never changed. Only the message latency was reduced by a factor of 250 times between 1993 and 2014, caused by kernel improvements and hardware development. Maybe this decision should be reviewed in favor of the also long known Message Passing Interface (MPI). This paper will give an introduction to the two message passing models to name theoretical problems which will come up in the case of using MPI as a IPC replacement.

### 1. INTRODUCTION

Since the microkernels came up, the message passing was always done by the Interprocess Communication (IPC). Now that the microkernels are about 35 years old [Mic14] and the ways to pass messages inside a kernel have developed, it could be time to check whether a replacement is advisable. This paper will introduce the Message Passing Interface (MPI) and the actual dominant male Interprocess Communication (IPC) in the way it is implemented in the actual L4 microkernel family. A comparison of these technologies and a feasibility study with all detected problems and possible solutions for them is shown at the end of this paper. This list could possibly be incomplete and was not tested by a real implementation. They are generated out of theoretical work and should be proved practically.

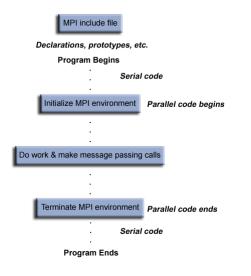

#### 2. MESSAGE PASSING INTERFACE (MPI)

The Message-Passing-Interface (MPI) is a specification which tries to solve the problem between portability, efficiency and functionality. The development of MPI began in the year 1992 based on existing ideas and libraries for communication. Today the most recent MPI version is MPI-3 [Mes12]. MPI should not be recognized as an implementation, more as a library which defines return values, functions

WAMOS '2014 Wiesbaden, Germany

B. Sc. Lasse Löffler Wiesbaden University of Applied Science Department DCSM Unter den Eichen 5 Wiesbaden, Germany lasse.loeffer@gmail.com

and parameter. Based on this library, there are many existing open- and closed source implementation for different programming languages. The fact that all are implemented along this specification makes them compatible. Originally MPI was designed for distributed shared memory (DSM) architectures, which were becoming popular at the time when MPI was developed. As the architecture trends changed towards Non-Uniform Memory Access (NUMA) and No Remote Memory Access (NoRMA), MPI was adapted. Since this day MPI was able to handle both architectures seamlessly and transparently to the developer. Today MPI runs on virtually any available hardware platform. This is solved by maintaining a distributed shared memory architecture regardless of the underlying physical circumstances of the machine [Wil07] [Mic]. A reason for using MPI could be one of the following:

- Portability: Only a little or no work to do if a application is ported from one MPI conform platform to another.

- Standardization: MPI is a message passing library which could be declared as a standard. MPI is supported by the most current available platforms and has replaced many other competitors over the years.

- Performance: Most of the MPI implementations are well developed and tested over many years. MPI is used in the context of parallel programming, so it was optimized to gain a high throughput of messages.

- Functionality: There are about 435 routines defined in the current MPI-3 standard, which includes the majority of the older MPI standards.

#### 2.1 Point-to-Point Communication

The MPI point-to-point functionality typically invokes message passing between two different MPI tasks. Two tasks running on the same host (or even inside same process) do not know anything of the other side process. MPI communication has one explicit sender and another task which is performing the receive operation. MPI has different routines for sending and receiving messages [Bla14].

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

Copyright 2014 ACM X-XXXXX-XX-X/XX/XX ...\$15.00.

These are for example:

- Blocking send / blocking receive

- Non-blocking send / non-blocking receive

- Combined send and receive

The perfect case of communicating is that both sides of communication are present at one time. This is often called a rendezvous. But this is rarely the case in the real world. Somehow the implementation of MPI must handle the general case of being not present when the other side wants to send or deliver a message. For this case MPI manages a system buffer to meanwhile save the messages. This MPI buffer is handled by the implementation and is not accessible by the user or any programmer. This buffer could be generated on both sides (sender and receiver). As said before, MPI has got two types of communication, the blocking and non-blocking operations. Most of the MPI routines could be used either one or the other way [Bla14]. These two types will be described in the following points:

**Blocking Operations:**

- Will only "return" if it is safe to possibly change the application buffer (where the send data is located) and the receiver's data is not influenced by continuing computation.

- A blocking send can be a rendezvous between the two threads, which means that there is some kind of handshaking between the two processes.

- A blocking send operation could possibly be asynchronous if the system buffer of the receiving thread could be used to hold the messages.

- A blocking receive only "returns" after the data is transferred and available for this processes.

Non-blocking:

- Non-blocking operations return to the caller immediately, because it is not necessary to wait on communication events to complete.

- These operations only request the MPI library to perform a send operation to the receiving partner when it is available.

- Non-blocking operations are mostly used to avoid loosing computation time while waiting for a synchronous operation.

- MPI provides functions to check whether a message was delivered or is still waiting in the system buffer.

Another feature of MPI is that messages are transmitted in the right order by guarantee. It is not possible that a message overtakes another. Messages which are sent first will be received first.

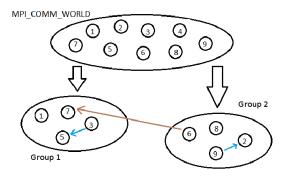

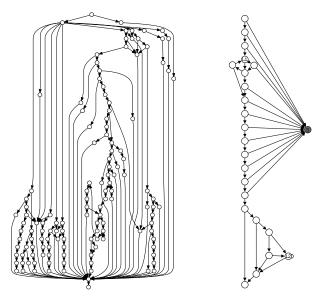

#### 2.2 Group and Communicator

There are two control mechanisms inside the MPI specification to guarantee a collision free communication. A group is an abstract to combine MPI processes which are performing the same computational operation. A process could belong to more than one group, but has a unique identifier in every group. The other mechanism is called the communicator, which could be separated into intra-communicator and inter-communicator. A communicator is responsible for handling communication operations for the processes of a group. As simply could be imagined, the intra-communicator handles communicator of processes inside the group, while the intercommunicator handles the communication with processes of other groups. A communicator which is always available is the MPL\_COMM\_WORLD, where all processes belong to. The whole group and communicator design of MPI is shown on figure 1.

Figure 1: Overview of the MPI group and communicator mechanism.

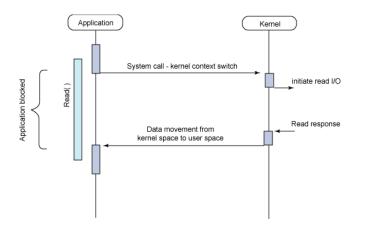

### 3. INTERPROCESS COMMUNICATION (IPC)

In an operating system the kernel is the most important object, which is normally separated in two parts: the kernel space (privileged mode) and the user space (unprivileged mode). The early monolithic kernel concepts all the basic system services, like file system, memory management, I/O communication and interrupt handling are being executed in the privileged mode. Today's monolithic kernels have got a layered design, which can be found from the basic process management up to the high level interfaces of the kernel space. The issue is that all the basic services are running in privileged mode causing serious problems, i.e lack of extensibility, large kernel size and bad maintainability [J. 06].

At this point the microkernel concept was born. The idea of the microkernel is to increase the reliability by providing only the basic process communication and I/O control inside the kernel space and moving the other system services into the user space. The system services inside the user space are a form of normal processes, so called servers. On the other hand the basic servers are not longer inside the kernel space and therefore the microkernel needs a concept to allow communication between the servers by entering the privileged mode with a context switch. The servers are separated processes with their living environment. To open a communication channel, the microkernel needs a mechanism to allow an Interprocess Communication. Therefore the so called IPC mechanism is used [Raf]. IPC is not only a part of a microkernel and can also be found in a monolithic kernel like Linux. Normally in a monolithic kernel a process is the representation of a program in memory. In the microkernel context a process is called as task. The smallest section of virtual parallel execution of a program is called thread in both environments. The IPC mechanism differs between

tasks and processes. In the process context the communication is often done without the kernel via a pipe. In the task context a IPC via the kernel is always necessary [Dav99].

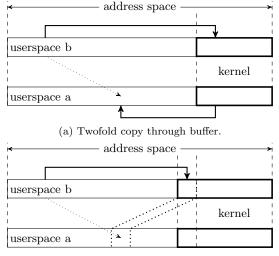

The IPC communication in the microkernel is done via messages. A microkernel has smaller code than a monolithic kernel, because basic services are moved into the user space. That means for the microkernel that it has to pass around more messages and the IPC performance has a very significant role in execution time. This is one of the issues of the microkernel against a monolithic kernel, because a monolithic kernel has no boundaries for the address space and can push easily pointers around. Microkernels use the message queue and several other techniques to communicate between servers, tasks and the kernel itself [Dav99]. The idea of IPC inside a microkernel is to create communication between threads and tasks in different address spaces. Each message in a microkernel has got a message tag and an optional list of message data. The message is passed from the sender's MessageData register to the kernel and the kernel copies the message unbuffered to the receiver's MessageData register. The communication is normally synchronized which means that the microkernel only delivers messages when the receiving thread is ready for receiving. The sending thread is blocked until the message is successfully delivered or a defined timeout has been reached [Ste].

The two fundamental IPC operations in a microkernel are send and receive. The send operation delivers messages from the calling thread to a destination thread, while the receive operation requests a message from another thread. The IPC messages can be marked with a flag whether the operation is blocking or non-blocking. If an IPC message is blocking, the IPC and the thread is blocked until the destination thread has performed the receive request. On the other hand, a non-blocking operation fails immediately if the target thread is currently not ready for receiving the IPC message. To reduce the IPC overhead on the microkernel the IPC operations can be combined, which means that sending and receiving is done in one operation [Raf]. In this case the thread sends the message data to the destination and waits for a reply, which saves time by saving one context switch.

To identify a thread or task in a microkernel environment, the kernel holds lists with capabilities. Capabilities represent an address of the destination thread or task. It is comparable with IP addresses at a TCP/IP network. Capabilities are not only an address of a destination, they can also represent permissions to access services. Each server inside the user space has got a capability. For example if a task needs to access the USB driver which is running in user space, than the task will be able to request the capability from the kernel. The kernel looks up if the task has the permission to access the USB driver and sends the capability to access the USB driver to the task. Now the task can start the IPC communication with the USB driver. If a task tries to send IPC messages to a capability without the permission, the kernel would terminate this task because this IPC communication is transferred and checked inside the kernel. IPC Messages in a microkernel environment are not only byte transfers. A message can also contain a capability of a server or interrupt notification from the kernel. The IPC communication is used for nearly every event, which

happens in the kernel or user space. A IPC message can transfer address space or regions and is used to handle page faults or exceptions from a thread.

# 4. COMPARISON

Generally said the Message Passing Interface (MPI) and the Interprocess Communication (IPC) are both ways to pass messages between processes. The first impression of analogousness is changed the more detailed this topic is considered.

MPI could be considered as a kind of API library, whereas IPC is more a single system call. The communication of IPC works with an unbuffered bidirectional queue, which could be filled with information by tasks. The whole communication of IPC is managed inside the microkernel in privileged mode. These interactions could be explained with copying messages over a shared memory segment. The MPI is able to interact over a network or with a shared memory concept. The message passing inside MPI is made transparent to the developer, whether it is done via network or inside the memory of a local machine. Both technologies support a simple one-to-one communication in a blocking and non-blocking way. In addition, MPI has got more functions which allow more comfort to the developer. MPI is able to perform 1-to-n and n-to-1 operations via one simple function call.

The two message passing ways differ in handling the nonblocking communication. While MPI stores the message in a buffer until the receiver will pick it up, IPC fails and returns after a defined timeout. So it could be possible that a MPI communication will sleep and wait forever for the receiver to get the message, whether IPC would return with a failure.

The data structures of MPI are defined by the kind of data which is passed around. MPI has got no clear data structure which must be used by the developer of an application. The default MPI specification includes all primitive types such as int, char, double. But with a simple data-type definition, MPI can transfer own created structs. If a MPI message is sent, the data is copied into a MPI message structure and then is passed to the target.

IPC has got a fixed message register structure, which is stored in the UTCB to transfer data between services. Normally the IPC message contains a tag and an array with pointers into the memory. The IPC tag defines the meta data with flags, source and destination and the array with the payload of the message.

MPI comes with the ability to handle groups of processes. A MPI process could generate new processes and organize them in new groups. Each process could theoretically communicate with every other MPI process in the MPI environment via a communicator.

The speed of MPI was measured on an eight cores (2.53 GHz dual quad-core) and 12 GB main memory machine. The CPUs are based on Westmere architecture and run in 64 bit mode. The nodes support 16x PCI Express Gen2 interfaces and are equipped with Mellanox ConnectX-2 QDR HCAs with PCI Express interfaces. The nodes are connected using a 36 port Mellanox QDR InfiniBand switch. The operating system used was RedHat Enterprise Linux Server release 5.4 (Tikanga). The processes were bound to core 1 on both nodes. The speed was measured with 1.6  $\mu$ s for a 1 byte message. The execution time is nearly constant until the message reaches a size of 64 byte. After this point the time rises until a message with 1k byte takes 4  $\mu$ s to be delivered [Dha11]. The speed parameters of the IPC are looking very different. Back in the year 1993 Liedtke [Joc93] described the "IPC dilemma" which was characterized by an IPC message delivery time of about 100  $\mu$ s. Also he described a way to get a twentyfold improvement, which means that an IPC took about 5  $\mu$ s. These two values were measured on a 50 MHz machine with a L3 microkernel running on it. Today's time values for IPC communication are about 185 CPU cycles on a 532 MHz (= 532,000,000 cycles per second) machine. This means an approximately time of a about  $0.34 \ \mu s$ . This time was measured with the UNSW/NICTA L4 Kernel seL4 [Kev13]. So without calculating the cycle time of the MPI measurement it is obviously that the IPC calls are much faster than the MPI ones.

#### 5. FEASIBILITY OF SUBSTITUTION

Depending on section 4 both concepts look very different. But as we have already seen, there are some issues that need to be fixed or worked around to be able to use MPI as the new IPC in the microkernel context.

The first issue which has to be taken care of is the fact that MPI doesn't have a capability feature. As the MPI section has shown, MPI allows per default every process to send a message to another. This is a security issue in the microkernel context and is managed via capabilities in the IPC context by the kernel. This issue could be worked around by programming the communicator of MPI that only processes of the same group could communicate with each other. So let's for example assume having three processes. Process A is the memory manager which has to send messages to every other process. Process B and C are user processes. To prevent process B from sending messages to process C the simply group structures shown below are implemented:

- Group 1: process A and process B

- Group 2: process A and process C

With the pre-condition from above, it would be possible for process B and C to send a message to process A (our memory manager) and receive a reply. It wouldn't be possible for process B to contact C or the other way around. With this condition it is possible to build a specific kind of capabilities. Also the fact of accessing resources could be managed with this strategy. Let's consider resources as a communication partner outside e.g. group 1. So if process B would access a resource outside the group there has to be a message sent to the communicator of group 1. At this point (the communicator) can be implemented as a kind of security management which will hold some something like access lists. Another way to solve this problem is to design resources as a communication partner which could be added to a group like our memory manager process A. Designing this fact in this way would also drown the problem of broadcasts or 1-to-n messages. The communicator of a group could also check if there is a permission to do so.

Another fact that has to be thought about and solved is the whole MPI message handling. In the non-blocking case there is a huge issue caused by the fact, that memory space is allocated to save the message until the receiver is available. This could be used by a malicious user-level program to perform a denial of service attack against the microkernel with the ability to send an unlimited amount of messages. This lesson was first learned by the developers of the Mach microkernel and was mentioned by Liedtke on many conferences. This was one of the reasons why Liedtke was anxious to only allow unbuffered messages.

In the blocking case there are some more facts to be taken care of. The first is that a process which is sending with a blocking system call could get stuck forever if the receiver is never concerns to appear to the rendezvous for message transferring. A real solution for this problem could lead to dramatic overhead of administrate some kind of timers or something else to quit the send operation. Also this maybe handled in the communicator, but the communicator does not have enough power to cancel a sent operation. This could be a possible solution, if the communicator is able to answer every blocking message operation which has been sent to him. As already said in the MPI chapter every message sending must be done via the communicator. So the communicator is implemented with the ability to answer the blocking messages with a failure after a defined time x (some kind of time out) which will cancel the process blocking.

The last two "issues" which have to be named is the performance of the MPI calls. As shown in the last chapter IPC is definitely faster than a MPI call. This would slow down the microkernel dramatically. A real workaround for this could not be named because the MPI implementations were tuned very hard in the last years, so there may be not more potential to optimise them. The other fact is, that the implementation of MPI has got much more code than the implementation of IPC. So the code in the microkernel would rise definitely and also there has to be more trusted and checked source code.

#### 6. CONCLUSIONS

As the comparison of this paper showed, the difference between MPI and IPC are not that serious as the first impression after the presentation of the different technologies could have indicated. Some of the differences like the buffering problem for MPI could easily be solved in the microkernel context. The bigger problems like the missing capabilities in MPI could lead to real problems in the implementation of MPI for microkernels. Also the fact, that a denial of service attack is possible is a very critical disadvantage of MPI. In the feasibly chapter some ideas are shown to handle these problems in a, more or less, easy way. For some problems no solutions could be named, so that they have to be accepted in the case of replacement.

To summarize, it can be said that there could be a possible chance of replacing IPC with a implementation of MPI. That this should be possible is showed by a MPI based microkernel called PARAM9000<sup>1</sup>. The only fact that would make this idea not practicable is that the MPI calls are not

<sup>&</sup>lt;sup>1</sup>http://www.cloudbus.org/~raj/

as efficient as the IPC ones and that the microkernel could be killed by an user-level program. Maybe MPI would be more useful if this issues are solved somehow. Up to now the replacing IPC by MPI in the microkernel context is not advised and meaningful.

### 7. REFERENCES

- [Bla14] Blaise Barney. Message Passing Interface (MPI), 2014. Available online at https://computing.lln.gov/tutorials/mpi/; visited on January 10th 2014.

- [Dav99] David A. Rusling. Inter process communication mechanism, 1996-1999. Available online at http://tldp.org/LDP/tlk/ipc/ipc.html/; visited on January 11th 2014.