## **MIPS-Light Instruction Set Summary**

The MIPS-Light ISA is a stripped down version of the MIPS R2000 ISA which is very close to the DLX ISA that is described in the textbook. The main difference between MIPS-Light ISA and DLX ISA concerns the branch instructions. MIPS-Light allows branches that have equal and not-equal comparisons between any two registers. When one of the registers is  $_{\text{IO}}$ , the branch instruction is equivalent to a  $_{\text{BGEZAL}}$ , which are not implemented in the MIPS-Lite Verilog model.

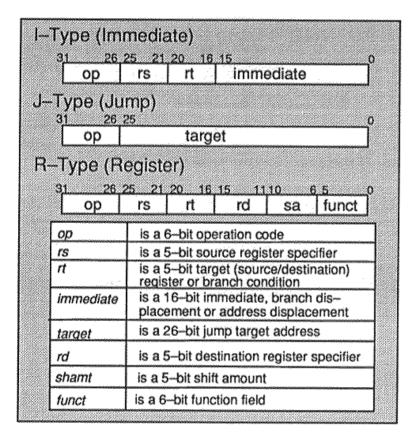

### 5.0.1 Instruction Formats

In addition to the standard R2000 formats shown above, the MIPS-lite instruction set also has an additional format for the bltz and bgez instructions:

Bit: [31-26] [25-21] [20-16] [15-0] Field: op=REGIMM rs sub offset

### 5.0.2 Load and Store Instructions

| Instruction | Format and Description op base rt offset                                                                                                                    |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load Word   | LW rt,offset(base) Sign-extend 16-bit offset and add to contents of register base to form address. Load contents of addressed word into register rt.        |

| Store Word  | SW rt,offset(base) Sign-extend 16-bit offset and add to contents of register base to form address. Store the contents of register rt at addressed location. |

### 5.0.3 ALU Instructions

1 of 5 18/11/13 11:33

| Instruction                            | Format and Description op rs rt immediate                                                                                                                                                           |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD Immediate                          | ADDI rt,rs,immediate Add 16-bit sign-extended immediate to register rs and place the 32-bit result                                                                                                  |

|                                        | in register rt. Trap on 2's-complement overflow.                                                                                                                                                    |

| ADD Immediate<br>Unsigned              | ADDIU rt,rs,immediate Add 16-bit sign-extended immediate to register rs and place the 32-bit result                                                                                                 |

|                                        | in register rt. Do not trap on overflow.                                                                                                                                                            |

| Set on Less Than<br>Immediate          | SLTI rt,rs,immediate Compare 16-bit sign-extended immediate with register rs as signed 32-bit integers. Result = 1 if rs is less than immediate; otherwise result = 0. Place result in register rt. |

| Set on Less Than<br>Immediate Unsigned | SLTIU rt,rs,immediate Compare 16-bit sign-extended immediate with register rs as unsigned 32-bit                                                                                                    |

| manediate onsigned                     | integers. Result = 1 if rs is less than immediate; otherwise result = 0. Place result in register rt.                                                                                               |

| AND Immediate                          | ANDI rt,rs,immediate Zero-extend 16-bit immediate, AND with contents of register rs and place the result in register rt.                                                                            |

| OR Immediate                           | ORI rt,rs,immediate                                                                                                                                                                                 |

|                                        | Zero-extend 16-bit <i>immediate</i> , OR with contents of register <i>rs</i> and place the result in register <i>rt</i> .                                                                           |

| Exclusive OR                           | XORI rt,rs,immediate Zero-extend 16-bit immediate, exclusive OR with contents of register rs and                                                                                                    |

| mmediate                               | place the result in register rt.                                                                                                                                                                    |

| Load Upper<br>Immediate                | LUI rt,immediate                                                                                                                                                                                    |

|                                        | Shift 16-bit <i>immediate</i> left 16 bits. Set least significant 16 bits of word to zeros. Store the result in register <i>rt</i> .                                                                |

2 of 5

| Instruction                  | Format and Description op rs rt rd sa function                                                                                                    |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Add                          | ADD rd,rs,rt                                                                                                                                      |

|                              | Add contents of registers <i>rs</i> and <i>rt</i> and place the 32-bit result in register <i>rd</i> . Trap on 2's-complement overflow.            |

| Add Unsigned                 | ADDU_rd,rs,rt                                                                                                                                     |

|                              | Add contents of registers <i>rs</i> and <i>rt</i> and place the 32-bit result in register <i>rd</i> . Do not trap on overflow.                    |

| Subtract                     | SUB rd,rs,rt                                                                                                                                      |

| Guottaut                     | Subtract contents of registers rt from rs and place the 32-bit result in register rd. Trap on 2's-complement overflow.                            |

| Subtract Unsigned            | SUBU rd,rs,rt                                                                                                                                     |

| Cubitact Chaighte            | Subtract contents of registers rt from rs and place the 32-bit result in register rd. Do not trap on overflow.                                    |

| Set on Less Than             | SLT rd,rs,rt Compare contents of register rt to register rs as signed 32-bit integers. Result = 1 if rs is less than rt; otherwise result = 0.    |

| Set on Less Than<br>Unsigned | SLTU rd,rs,rt Compare contents of register rt to register rs as unsigned 32-bit integers. Result = 1 if rs is less than rt; otherwise result = 0. |

| AND                          | AND rd,rs,rt Bitwise AND the contents of registers rs and rt, and place the result in register rd.                                                |

| OR                           | OR rd,rs,rt                                                                                                                                       |

| On                           | Bitwise OR the contents of registers rs and rt, and place the result in register rd.                                                              |

| Evelueius OD                 | XOR rd,rs,rt                                                                                                                                      |

| Exclusive OR                 | Bitwise exclusive OR the contents of registers rs and rt, and place the result in register rd.                                                    |

| NOR                          | NOR rd,rs,rt                                                                                                                                      |

|                              | Bitwise NOR the contents of registers rs and rt, and place the result in register rd.                                                             |

3 of 5 18/11/13 11:33

| Instruction                           | Format and Description op rs rt rd sa function                                                                                                                                                                                |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift Left<br>Logical                 | SLL rd,rt,sa Shift the contents of register rt left by sa bits, inserting zeros into the low order bits. Place the 32-bit result in register rd.                                                                              |

| Shift Right<br>Logical                | SRL rd,rt,sa Shift the contents of register rt right by sa bits, inserting zeros into the high order bits. Place the 32-bit result in register rd.                                                                            |

| Shift Right<br>Arithmetic             | SRA rd,rt,sa Shift the contents of register rt right by sa bits, sign-extending the high order bits. Place the 32-bit result in register rd.                                                                                  |

| Shift Left<br>Logical<br>Variable     | SLLV rd,rt,rs  Shift the contents of register rt left. The low order 5 bits of register rs specify the number of bits to shift left; insert zeros into the low order bits of rt and place the 32-bit result in register rd.   |

| Shift Right<br>Logical<br>Variable    | SRLV rd,rt,rs Shift the contents of register rt right. The low order 5 bits of register rs specify the number of bits to shift right; insert zeros into the high order bits of rt and place the 32-bit result in register rd. |

| Shift Right<br>Arithmetic<br>Variable | SRAV rd,rt,rs  Shift the contents of register rt right. The low order 5 bits of register rs specify the number of bits to shift right; sign-extend the high order bits of rt and place the 32-bit result in register rd.      |

# 5.0.4 Jump and Branch Instructions

| Instruction               | Format and Description op target                                                                                                                                                                                                                 |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Jump                      | J target Shift the 26-bit target address left two bits, combine with high order four bits of the PC, and jump to the address with a 1-instruction delay.                                                                                         |  |

| Jump And Link             | JAL target Shift the 26-bit target address left two bits, combine with high order four bits of the PC, and jump to the address with a 1-instruction delay. Place the address of the instruction following the delay slot in r31 (Link register). |  |

| Instruction               | Format and Description op rs rt rd sa function                                                                                                                                                                                                   |  |

| Jump Register             | JR rs Jump to the address contained in register rs, with a 1-instruction delay.                                                                                                                                                                  |  |

| Jump And Link<br>Register | JALR rs, rd  Jump to the address contained in register rs, with a 1-instruction delay. Place the address of the instruction following the delay slot in register rd.                                                                             |  |

**ERRATA:** The correct JALR instruction format is:

JALR rd, rs

| Instruction                                         | Format and Description                                                                                                                                                             |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Branch on Equal                                     | BEQ rs,rt,offset op rs rt offset                                                                                                                                                   |

|                                                     | Branch to target address if register rs is equal to register rt.                                                                                                                   |

| Branch on Not<br>Equal                              | BNE rs,rt,offset Branch to target address if register rs is not equal to register rt.                                                                                              |

| Branch on Less than or Equal Zero                   | BLEZ rs,offset Branch to target address if register rs is less than or equal to zero.                                                                                              |

| Branch on Greater<br>Than Zero                      | BGTZ rs,offset Branch to target address if register rs is greater than zero.                                                                                                       |

| Branch on Less                                      | BLTZ rs,offset REGIMM rs sub offset                                                                                                                                                |

| Than Zero                                           | Branch to target address if register rs is less than zero.                                                                                                                         |

| Branch on Greater<br>than or Equal Zero             | BGEZ rs,offset Branch to target address if register rs is greater than or equal to zero.                                                                                           |

| Branch on Less<br>Than Zero And Link                | BLTZAL rs,offset  Place address of instruction following the delay slot in register r31 (Link register). Branch to target address if register rs is less than zero.                |

| Branch on Greater<br>than or Equal Zero<br>And Link | BGEZAL rs,offset  Place address of instruction following the delay slot in register r31 (Link register). Branch to target address if register rs is greater than or equal to zero. |

5 of 5