# **Copyright Notice**

## These slides are distributed under the **Creative Commons Attribution 3.0 License**

You are free:

- to share—to copy, distribute and transmit the work

- to remix—to adapt the work

under the following conditions:

**Attribution:** You must attribute the work (but not in any way that suggests that the author endorses you or your use of the work) as follows: "Courtesy of Gernot Heiser, UNSW Sydney"

The complete license text can be found at http://creativecommons.org/licenses/by/3.0/legalcode

1 COMP9242 2019T2 W03b

© Gernot Heiser 2019 – CC Attribution License

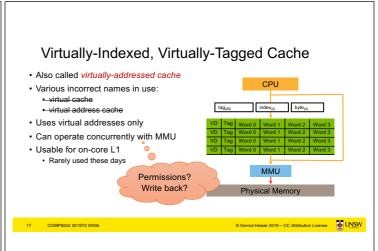

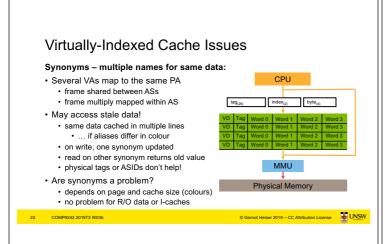

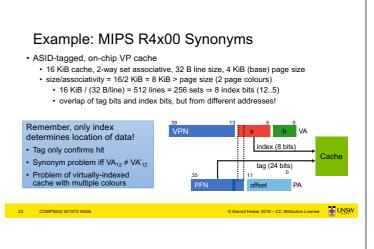

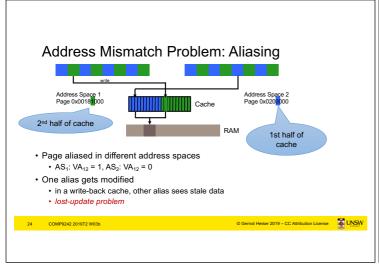

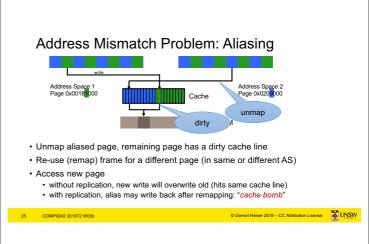

## Summary: VV Caches ☑Fastest (don't rely on TLB for retrieving data) ₩... or alternative mechanism for providing protection #still need TLB lookup or physical tag for writeback **Suffer from synonyms and homonyms** Historically used with shallow hierarchies to support bigger L1 may even be required on kernel → user switch · ... or guarantee no synonyms and homonyms • Used on MC68040, i860, ARM7/ARM9/StrongARM/Xscale • Used for I-caches on several other architectures (Alpha, Pentium 4) · Not used on recent architectures nse 🐺 UNSW

# Summary: ASID-Tagged VV Caches • Add ASID as part of tag • On access, compare with CPU's ASID register • Removes homonyms • potentially better context-switching performance #ASID recycling still needs flush #Doesn't solve synonym problem (but that's less severe) #Doesn't solve write-back problem • Not used on recent architectures

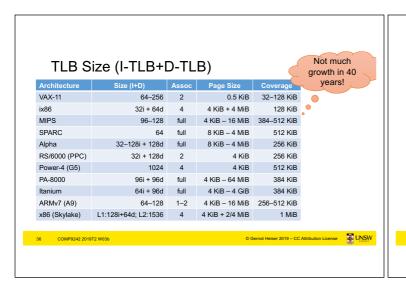

# **TLB Size**

### TLB coverage

- · Memory sizes are increasing

- · Number of TLB entries are roughly constant

- · Base page sizes are steady

- 4 KiB (SPARC, Alpha used 8KiB)

- · OS designers have trouble using superpages effectively

- · Consequences:

- Total amount of RAM mapped by TLB is not changing much

- Fraction of RAM mapped by TLB is shrinking dramatically!

- Modern architectures have very low TLB coverage!

- The TLB can become a bottleneck

37 COMP9242 201912 W03b G Gemot Helser 2019 – CC Attribution License UNSW

## Reminders

- AOS Prize for top performer in this course

- OS Hall of Fame for straight HDs in OS, AOS, Dist Syst, Thesis

- If you want a t-shirt, design one!

COMP8242 2019T2 W03b © Gemot Heiser 2019 – CC Attribution License