School of Computer Science & Engineering

**COMP9242 Advanced Operating Systems**

2020 T2 Week 07b

**Security: Information Leakage**

@GernotHeiser

Spectre/Meltdown material courtesy of Yuval Yarom (UAde) & Daniel Genkin (UMI)

### Copyright Notice

#### These slides are distributed under the **Creative Commons Attribution 3.0 License**

- · You are free:

- to share—to copy, distribute and transmit the work

- to remix—to adapt the work

- under the following conditions:

- Attribution: You must attribute the work (but not in any way that suggests that the author endorses you or your use of the work) as

"Courtesy of Gernot Heiser, UNSW Sydney"

The complete license text can be found at http://creativecommons.org/licenses/by/3.0/legalcode

COMP9242 2020T2 W07b: Information Leakage

© Gernot Heiser 2019 - CC Attribution License

# **Timing Channels**

Principles

# Refresh: Timing Channels

#### Information leakage through timing of events

Typically by observing response latencies or own execution speed

Covert channel: Information flow that bypasses the security policy

Side channel: Covert channel exploitable without insider help

### **Causes of Timing Channels**

#### Algorithmic

if (secret) { short\_operation(...); } else { long\_operation(...); OS problem or not?

#### **Resource Contention**

- Software resources

- · OS abstractions

- · buffer cache...

- Hardware resources

- · caches etc

- not visible at ISA (HW-SW contract)

Microarchitectural timing channels

Affect execution speed

COMP9242 2020T2 W07b: Information Leakage

© Gernot Heiser 2019 - CC Attribution License

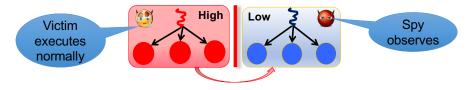

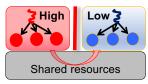

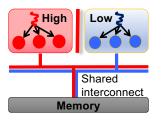

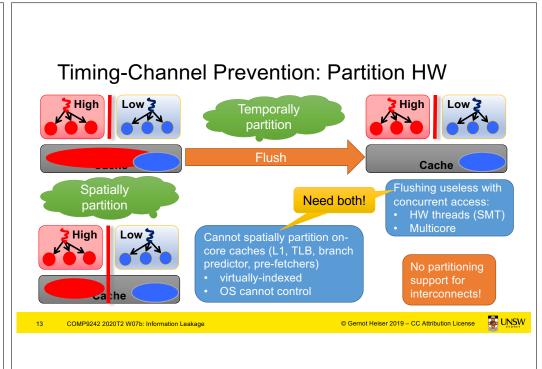

### Shared Hardware: Stateless Interconnect

#### H/W is bandwidth-limited

- Interference during concurrent access

- Generally reveals no data or addresses

- Must encode info into access patterns

- Only usable as covert channel, not side channel

COMP9242 2020T2 W07b: Information Leakage

© Gernot Heiser 2019 - CC Attribution License

### Shared Hardware: Stateful Resources

H/W is capacity-limited

- Interference during

- · concurrent access · time-shared access

- Collisions reveal addresses

- Usable as side channel

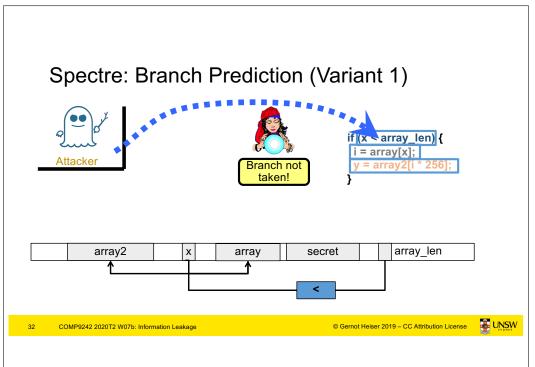

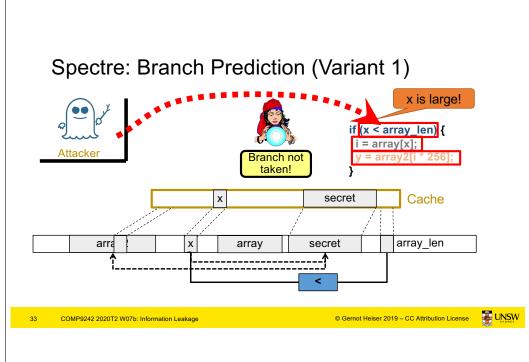

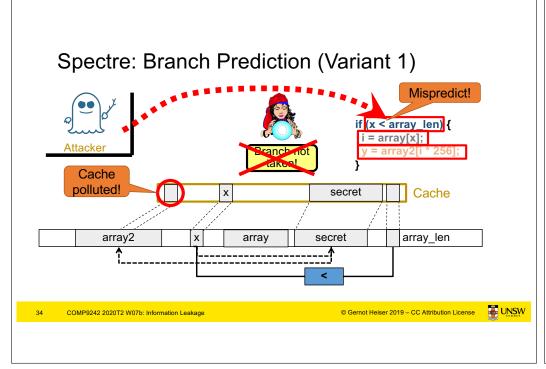

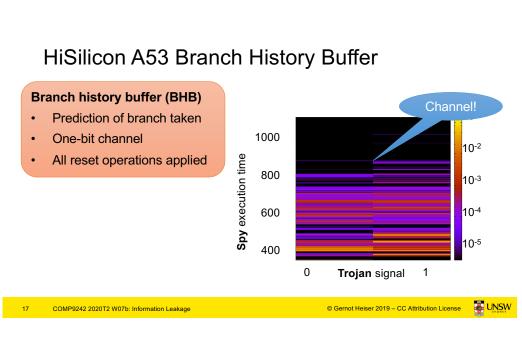

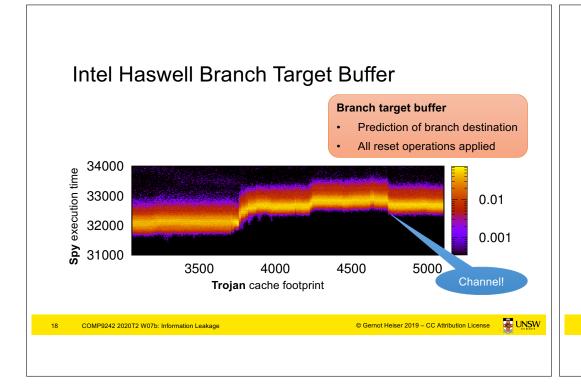

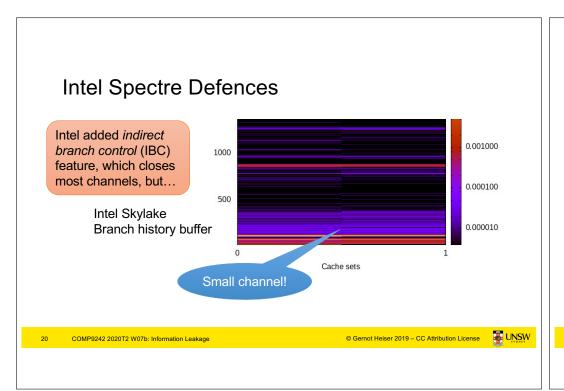

### Can be any state-holding microarchitectural feature:

- · CPU caches

- branch predictor

- pre-fetcher state machines

# **Timing Channels**

Example: LLC Side Channel

## Challenge: Slow LLC Access Times

- L1 (32 KiB) probe:

- 64 sets \* 8 ways \* 4 cycles = 2,048 cycles

Probing entire LLC is too slow, but single set is fast

- Small last-level cache (6 MiB):

- 8,192 sets \* 12 ways \* ~30 cycles = ~3,000,000 cycles

- · Approach:

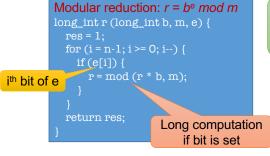

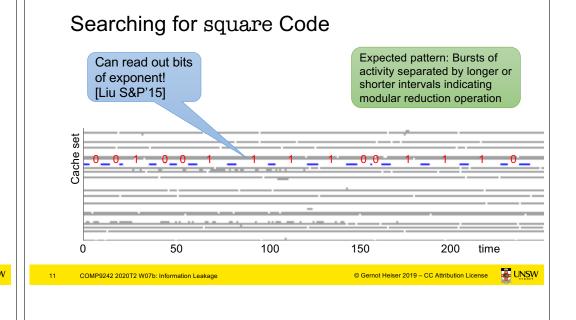

- **Example:** Look for square code in square-and-multiply exponentiation of GnuPG

- Probe one or a few cache sets at a time

- Find "interesting" sets ("eviction set") by looking for patterns

COMP9242 2020T2 W07b: Information Leakage

© Gernot Heiser 2019 - CC Attribution License

## Searching for square Code

COMP9242 2020T2 W07b: Information Leakage

Expected pattern: Bursts of activity separated by longer or shorter intervals indicating modular reduction operation

© Gernot Heiser 2019 - CC Attribution License

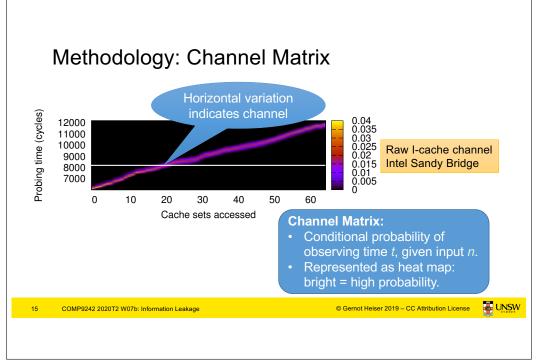

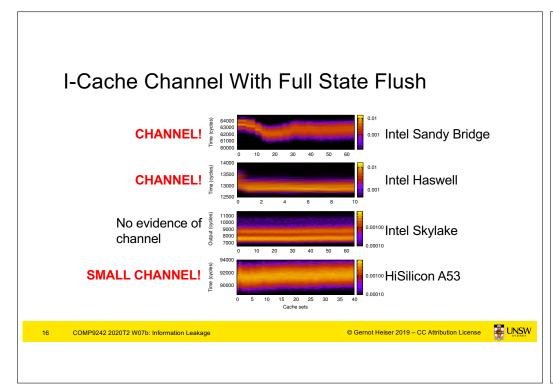

#### **Result Summary: Measured Capacities** Channel Sandy Bridge Haswell Skylake ARM A9 ARM A53 flush raw flush raw flush raw | flush raw | flush L1 D-cache 4.0 0.04 4.7 0.43 3.3 0.18 5.0 0.11 2.8 0.15 L1 I-cache 0.46 0.36 0.37 0.18 4.5 0.5 3.7 0.85 4.0 1.0 TLB 3.2 0.18 2.5 0.33 0.16 3.4 0.14 3.2 0.47 0.11 BTB 2.0 1.7 4.1 1.6 1.8 1.9 1.1 0.07 1.3 0.64 **BHB** 1.0 1.0 1.0\_1.0 1.0 1.0 1.0 0.01 1.0 0.5 Residual channels Uncloseable channel on each processor studied! COMP9242 2020T2 W07b: Information Leakage © Gernot Heiser 2019 - CC Attribution License

# **Speculating Desaster**

COMP9242 2020T2 W07b: Information Leakage

© Gernot Heiser 2019 - CC Attribution License

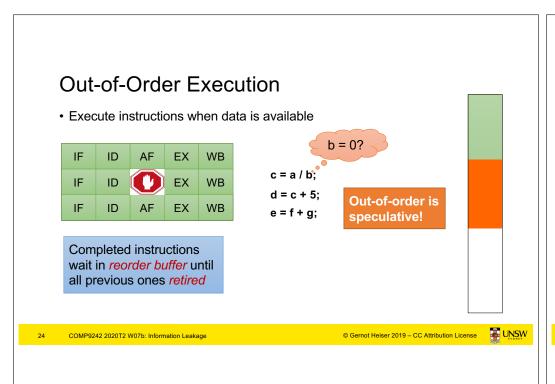

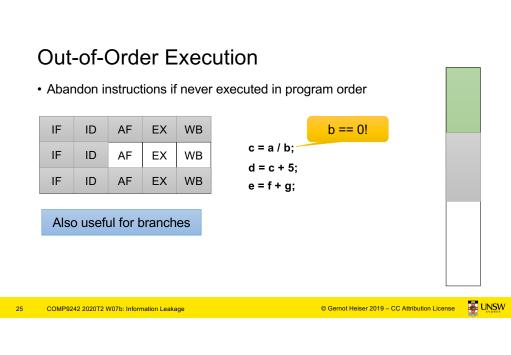

# Instruction Pipelining

- · Nominally, the processor executes instructions one after the other

- Instruction execution consists of multiple steps

- · Each uses a different unit

| Instruction<br>Fetch | Instruction<br>Decode | Argument<br>Fetch | Execute | Write Back |  |

|----------------------|-----------------------|-------------------|---------|------------|--|

|                      |                       |                   |         |            |  |

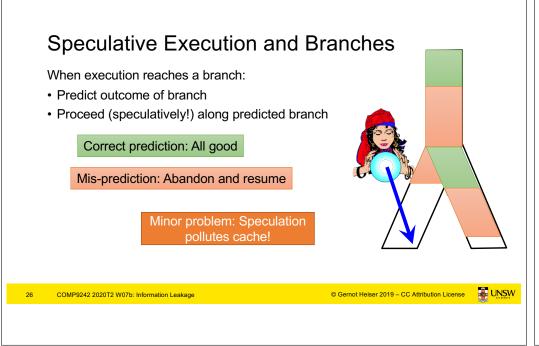

# Instruction Pipelining

- Nominally, the processor executes instructions sequentially

- Instruction execution consists of multiple steps

- · Each uses a different unit

- Pipelining concurrently instruction execution

Problem: **Dependencies**

| Inst fetch | Inst decode | Arg fetch | Execute | Write back |

|------------|-------------|-----------|---------|------------|

| Inst fetch | Inst decode | Arg fetch | Execute | Write back |

| Inst fetch | Inst decode | Arg fetch | Execute | Write back |

| Inst fetch | Inst decode | Arg fetch | Execute | Write back |

| Inst fetch | Inst decode | Arg fetch | Execute | Write back |

COMP9242 2020T2 W07b: Information Leakage

2(\$tp),\$tp \\$0,%rdx mov %rdx, \$A[1] mulq \$m1 add %rax,\$N[0] mov 8(\$a,\$j),%rax adc \\$0,%rdx add \$A[0],\$N[0] adc \\$0,%rdx mov \$N[0],-24(\$tp) mov %rdx, \$N[1] mulq \$m0 add %rax,\$A[1] mov 8\*1(\$np),%rax adc \\$0,%rdx mov %rdx, \$A[0] mulq \$m1 add %rax, \$N[1] mov (\$a,\$j), %rax mov 8(\$a,\$j),%rax adc \\$0,%rdD