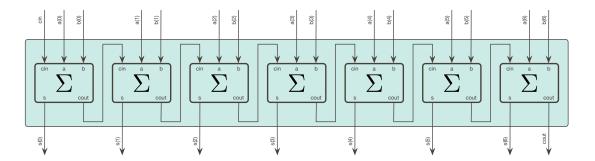

Abbildung 1: Ein Ripple-Carry Adder

Hardwarebeschreibungssprachen Wintersemester 2021/2022

Hochschule RheinMain Prof. Dr. Steffen Reith

## 1. Übungsblatt

Lösen Sie die folgenden Aufgaben:

- i) Installieren Sie ghdl und gtkwave auf Ihrer Arbeitsmaschine.

- ii) Packen Sie das mitgelieferte zip-Archiv aus. Ergänzen Sie die fehlenden Teile in der Datei FullAdder.vhd und FullAdder\_TB.vhd. Simulieren Sie den FullAdder mit ghdl (analyze, elaborate, run) und erzeugen Sie ein .vcd-File. Zeigen Sie die Simulationsergebnisse im .vcd-File mit gtkwave (Achtung: Wählen Sie den richtigen Zeitmaßstab um Ergebnisse zu sehen.) an. In Abbildung 1 sehen Sie 7 Volladdierer verdrahtet zu einem Ripple-Carry Addierer. Dort können Sie auch die einzelnen Ein- und Ausgabesignale eines Volladdierers sehen.

- iii) Ergänzen Sie RCAdder\_TB.vhd und RCAdder.vhd und führen Sie eine Simulation durch. Können Sie den Addierer mit allen möglichen Eingaben testen? Angenommen Sie sollen einen 64-Bit Addierer (statt des enthaltenen 8-Bit Addierers) testen. Welche Probleme tauchen dann auf?

- iv) Bauen Sie RCAdder. vhd um und entfernen Sie die generic-Anweisung und die for-Schleife. Das Resultat soll ein von Hand verdrahteter Ripple-Carry Addierer für 4 Bits sein. Wie ein Ripple-Carry-Addierer aufgebaut ist zeigt Abbildung 1. Simulieren Sie Ihren Addierer und überprüfen Sie dessen Korrektheit.

Besprechnung und Abnahme am 5. November 2021