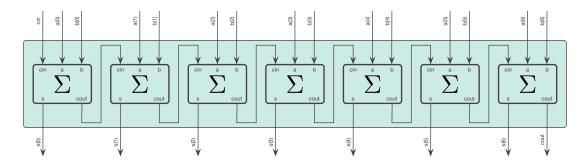

Abbildung 1: Ein Ripple-Carry Adder

Hardwarebeschreibungssprachen Wintersemester 2025/2026

Hochschule RheinMain Prof. Dr. Steffen Reith

## 1. Übungsblatt

Lösen Sie die folgenden Aufgaben:

- i) Installieren Sie auf Ihrem System ghdl (https://ghdl.github.io/ghdl/getting.html) und gtkwave (https://gtkwave.sourceforge.net/) auf Ihrer Arbeitsmaschine.

- ii) Installieren Sie den RISC-V Simulator *Ripes* (https://github.com/mortbopet/Ripes) auf Ihrer Arbeitsmaschine. Wählen Sie den "Single Cycle Processor" (Icon links oben in der GUI). Diesen werden wir im Laufe des Semesters implementieren.

- iii) Packen Sie das mitgelieferte zip-Archiv aus. Ergänzen Sie die fehlenden Teile in der Datei FullAdder.vhd und FullAdder\_TB.vhd. Simulieren Sie den FullAdder mit ghdl (Kommandos: analyze, elaborate, run) und erzeugen Sie ein .vcd-File. Zeigen Sie die Simulationsergebnisse im .vcd-File mit gtkwave (Achtung: Wählen Sie den richtigen Zeitmaßstab um Ergebnisse zu sehen!) an.

- iv) In Abbildung 1 sehen Sie 7 Volladdierer zu einem Ripple-Carry Addierer verdrahtet. Dort können Sie auch die einzelnen Ein- und Ausgabesignale eines Volladdierers sehen. Ergänzen Sie RCAdder\_TB.vhd und RCAdder.vhd und führen Sie eine Simulation durch. Können Sie den Addierer mit allen möglichen Eingaben testen? Angenommen Sie sollen einen 64-Bit Addierer (statt des enthaltenen 8-Bit Addierers) implementieren. Welche Probleme tauchen dann auf?

- v) Beschäftigen Sie sich mit Xilinx Vivado (kostenlose Version). Sollten Sie Probleme mit Plattenplatz haben, so installieren Sie nur die Artix7-Familie (kein Kintex, Virtex und Ultrascale). Wollen Sie die Laborrechner verwenden, dann beschäftigen Sie sich mit der Installation im Techniklabor.

- vi) Bringen Sie einen 4-Bit Addierer auf dem ausgeliehenen FPGA-Board<sup>1</sup> mit Hilfe von Vivado zum Laufen. Besonders wichtig ist das *richtige*. XDC-File<sup>2</sup> für Ihr Board. Dazu ist es sinnvoll die Schiebeschalter mit Eingängen und die Ausgänge mit LEDs zu verbinden.

Besprechnung und Abnahme am 5. November 2025

$<sup>^1\</sup>mathrm{z.B.}$  https://digilent.com/reference/programmable-logic/nexys-4-ddr/start

<sup>&</sup>lt;sup>2</sup>siehe https://github.com/Digilent/digilent-xdc/